快速、高效、多产?您的早期IC设计物理验证可以是所有的…

作者:约翰·弗格森,纳米恩·胡萨姆

随着每一个新的工艺节点的出现,都需要更复杂的要求来确保硅的工作。在集成电路(IC)物理验证的世界中,需求的增长意味着要运行更多的检查,要解析更多的错误,要纠正错误的编辑更多,要实现干净的设计的迭代更多,每次迭代的运行时间更长。作为西门子不断努力帮助设计公司尽快将新颖的芯片设计推向市场的一部分,Calibre设计解决方案部门实施了多种功能来支持左移策略,以帮助设计团队应对这些挑战并减少生产时间。

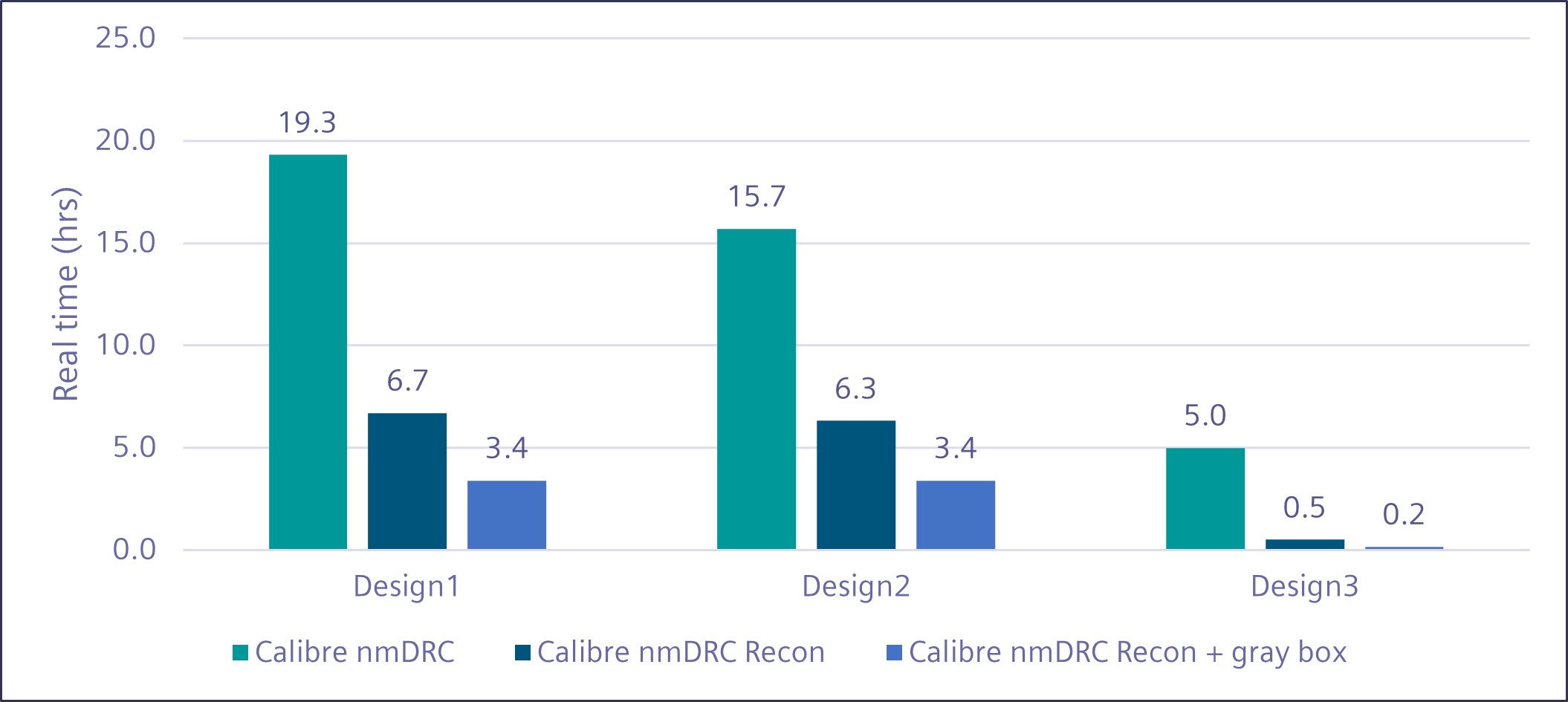

虽然左移策略中使用了许多工具和功能,但我们最近的论文,加快早期设计规则探索和物理验证,研究了Calibre nmDRC Recon和Calibre Auto-Waivers工具如何帮助设计公司加快和改善早期设计验证。Calibre nmDRC Recon工具允许设计团队运行一组选定的Calibre签收设计规则检查(DRC),通过专注于识别关键的早期系统设计错误,帮助减少早期/不完整设计数据的运行时间。在错误调试期间,Calibre Auto-Waivers工具使用了几个关键的新功能,不仅可以消除错误,还可以为设计团队提供有关实际错误的更多信息,以帮助设计人员在修复策略上做出快速、准确的决策。这两种功能都被许多世界领先的IC设计公司广泛采用,为设计人员提供了快速识别单个DRC错误的能力,而且还能快速识别负责任的基本设计缺陷。结合起来,这些工具和功能可以显著减少从早期/不完整的设计到准备试制所需的总时间和人工工作。

想了解更多吗?为了深入了解您的设计团队如何使用这些左移策略来更高效地运行早期IC设计验证,下载一份我们今天的报纸!