当我参加SPIE光刻会议时,我通常希望听到最新的技术,这些技术是下一个让我们跨越当前光刻障碍的技术。在这一点上,可能是EUV (还是会这样?吗?)

但是,追踪那些还没有在名字旁获得“是的,这可行”的离谱想法可能会更有趣;人们仍在推推搡搡,想知道从现在起两三个节点是否能满足我们的需求。

所以今年我想我应该去看看这两者都发生了什么定向自组装(DSA)和nanoimprint光刻(零)。这两种方法都在过去几年里出现并激增,我想我应该报告一些新的改进,关于哪些方法可行,哪些方法不可行。我从这次会议中做了笔记,并把它做成了一些东西,如果幸运的话,可能会像一个有趣的故事。

但有些这样的会议有一个问题:你会看到一堆会议。有些会议比其他会议组织得更好。IEDM做得特别好,他们要求会议主持人提前为媒体确定最有意义的会议,这样我们就有了重点关注的线索。另一方面,有些人只是简单地按时间顺序列出了他们所有的论文。因此,在浏览了15分钟那些令人麻木的标题之后(技术论文并不以吸引眼球的标题而闻名),你有点呆头呆脑,它们听起来都一样。

通常情况下,你处于两者之间,所以你仍然会发现自己意识到太迟了,你应该参加一个会议,但你没有参加。(公平地说,这些展会对媒体的关注程度各不一样……特别是SPIE直到展会结束几个月后才提供会议进程,除非你把整个事情都记录下来,否则不可能及时提供详细的报道……但他们的重点是他们的工程观众,而不是媒体。)

所有这些都是一个非常迂回的说法,就在事情接近尾声时,我发现有一篇论文我希望我能看到。它不仅报告了DSA的一些进展,也不仅仅是将NIL向前推进。不,它报告的是实际设备使用这两个DSA和NIL,一路上记录经验教训。这个结果并不值得投入生产,但它代表了一个巨大的飞跃,尽管是在一个非常特定的领域:硬盘驱动器。

这家公司是HGST,他们非常友好地回答了我的问题,并在事后发送了后续信息。他们的要求与IC设计师可能需要的要求不同——其中一些要求让他们休息一下,但其中一些要求比IC设计师的要求更艰苦。

因此,让我们从回顾HGST试图解决的问题开始。这些家伙想要做一个有尽可能多的存储空间的磁盘。传统上,使用连续磁性介质,用单个域定义位(或者更具体地说,极化之间的转换-或缺乏-定义位)。新的大想法是创造出磁性材料的孤岛。每一个都是一点。这种方法被称为比特模式媒体(BPM)。

挑战在于尺寸:我们说的是20nm范围-全音高,而不是半音高;我们说的是现在,不是三个节点之后。这需要光刻技术,而集成电路暂时还不需要。

岛屿的排列通常是“六角形紧密排列”(HCP),本质上是点的紧密排列;任何点周围都有六个相邻点。但是为了与现有的硬盘读头兼容,一个矩形岛的宽度略大于深度(即,比特面积比-或BAR大于1,可能小于2或3)将是更可取的。因此,虽然他们的一些早期作品反映了HCP布局,但他们在某个时候改变了矩形布局。(我提到过会有首字母缩写吗?)

因此,即使他们正在寻找比IC上使用的更激进的尺寸,他们也有一个非常有规律的模式-没有时髦的形状或FinFET废话,不仅需要更多的工作来掌握,而且还需要更多的工作EDA的帮助来定义DSA指南。只是一个数组。当然是圆形的,所以有周向尺寸和径向尺寸。

另一个关键的要求是成本:他们可以为这种新方法支付每个磁盘1美元的额外费用。所以所有东西都要超级便宜。问题是,使用能够提供这些尺寸的光刻技术进行生产可能会缓慢而昂贵。因此,我们的想法是花时间制作昂贵的母版,然后使用纳米压印技术(与Molecular imprint合作完成)将母版用于复制。

事实上,由于NIL模板通常被期望能够在磨损之前制作10,000份副本,因此主模板将制作10,000个工作模板,并且每个工作模板将用于制作实际的磁盘。然后,单个主机将启用1亿个磁盘。

这就为我们提供了制造的两个不同方面:创建母版和从母版复制。

是的,主人。

他们使用DSA来创建master,选择化学外延来引导自组装。需要提醒的是,这意味着化学痕迹被放置在衬底上作为引导,而不是使用引导“壁”(“石墨-外延”)。这使得图案可以不间断地覆盖在引线上;换句话说,导游做了他们的工作,但他们不碍事。

所以高层次的过程是:

1.使用电子束光刻(慢,但只用于大师)创建指南。

2.执行DSA步骤

一个沉积。

b。退火

c。发展

3.将DSA图案转移到衬底上。

DSA过程需要更多的讨论;这似乎是一个定义明确的事情,但实际上,这仍然是一个狂野的、模糊的世界,每个人都在试图找出正确的方法来做这件事。有很多选择,在这个过程中,HGST最终尝试了一些变化。他们报告了一些结果(自己保留了一些),并与芝加哥大学的研究人员合作研究了部分结果。我不会说得太详细,但有一些考虑是值得一提的。

首先是嵌段共聚物(BCP)的选择。有几种可供选择的共聚物,其中大多数是二嵌段共聚物,这意味着两个相邻的聚合物将自组装。PS-b-PMMA(聚苯乙烯和聚(甲基丙烯酸甲酯)-“b”代表“块”)似乎是最常见的。较少研究,但也可能是三嵌段共聚物-三组聚合物。在某些情况下,它只有两个聚合物,但中间聚合物的两端都与另一个相连:P2VP-b- ps -b-P2VP就是一个例子(P2VP是聚乙烯吡啶…我不知道2是什么…我没有想到这些东西)。

他们选择了PS-PMMA,因为它很容易显影(也就是说,很容易选择性地去除两种聚合物中的一种),而且它们形成垂直层状结构。这种选择的缺点是很难实现小于25纳米的音高;有些可以低到18纳米。他们想要更多的空间来定义小岛域,所以,正如我们将看到的,他们在转移阶段使用了线路加倍。

选择PS-b-PMMA后,DSA过程相对简单:沉积bcp,退火让它们自分离,然后显影——这意味着去除两者之一(PMMA),留下由PS定义的图案。

接下来的步骤——将该模式转移到基板中——是团队执行许多选项的地方。

- 直接蚀刻:PS作为掩模,将图案蚀刻到衬底上。

- “脱铬”:铬沉积,用湿条脱铬。PS上的部分优先脱落,留下直接在基板上的部分(PMMA被去除的地方)作为蚀刻掩模。这种方法在25nm波长下表现不佳,因此被放弃。

- “Cr+SOG剥离”:像Cr剥离一样,但玻璃在铬上旋转(“SOG”=“旋转玻璃”)。这在Cr发射失败的地方起了作用。

- 块选择性渗透(又名选择性渗透合成):使用原子层沉积(ALD)方法将未显影的表面暴露在三甲基铝(TMA)中,然后暴露在水蒸气中。这使得氧化铝优先于或实际上被PMMA吸收。PS被蚀刻掉,留下氧化铝作为硬掩膜。

- 电沉积:显影后电镀金属(如镍在钨籽上);金属位于PS线之间;然后PS被移除。这需要导电基板。

- 他们还使用了三嵌段共聚物,将沥青降至16纳米。

马金的副本

有了母版,就有了一些复制的选择。这里的第一个细节是“语调逆转”。在我看来,这是你的印记模板是消极的还是积极的问题。当被压入抗蚀剂时,脊会变成“通道”,最终会确定隆起或凹陷的区域吗?他们发现,反转色调——模板脊最终变成凹陷——提供了最好的结果。

他们做出的另一个决定是将压印过程分为两个:一个用于周向线,一个用于径向线。这意味着他们必须创造两个master(或“次master”)。因为岛屿会变得更宽(也就是说,沿着半径——这意味着圆形轨道会比沿着轨道的岛屿的大小略宽),然后他们可以在圆周模板上使用不那么激进的技术。

对于径向模板,PS-b-PMMA的选择不能让他们像他们想要的那样紧密。因此,他们使用了侧壁间隔加倍,就像对集成电路所做的那样,将其降至可靠的7纳米半间距-这是迄今为止报道的此类工艺的最小特征。

实际结果

在尝试了所有这些不同的方法后,他们通过以下选择获得了成功:

- 硅的主人;石英加工大师

- PS-b-PMMA

- 27nm pitch周向副母,采用Cr+SOG提升;没有行加倍

- 20.5 nm节距径向副母线,由41 nm节距线创建,然后将其加倍;转移是通过直接蚀刻,尽管他们后来开发了更好的替代方案。

- BAR约为1.3

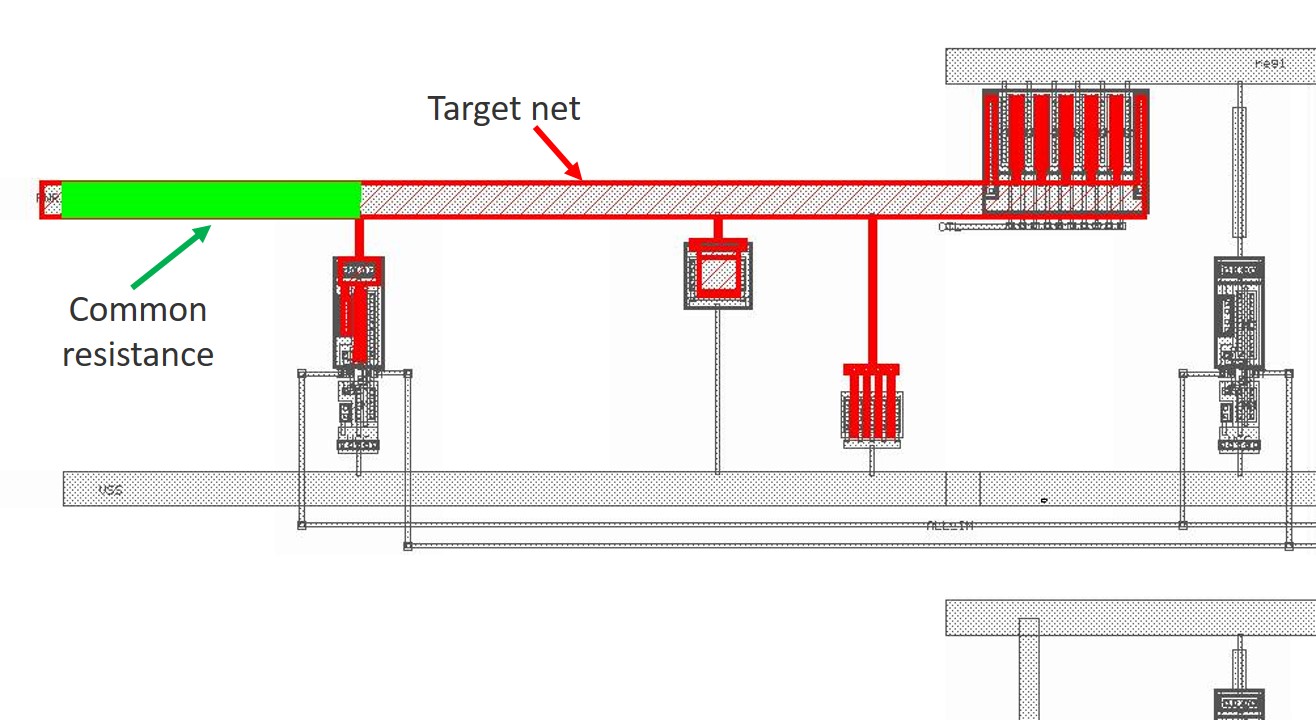

- 当压印到包含磁膜层的磁盘上时,先压印圆周线,然后是径向线,然后蚀刻出薄膜以创建磁岛。

你可以在他们的论文中找到更多细节,当收益可用时;这是论文8685-21,题为“~10纳米特征尺寸体系下大面积光刻图案的生成和转移”,Albrecht等人。

基于HGST在HDD项目上所做的工作,你如何看待DSA和NIL在ic上的发展——联合还是单独?