大多数人都熟悉TNG概念,它源自星际迷航电视剧被改名为“《星际迷航:原始系列”当它闪亮的继任者“《星际迷航:下一代班子草台”出现在现场(没有双关)。好吧,我被介绍给新一代的设计班子草台测试(DFT)。

在我之前的文章分布式芯片上的温度传感器提高性能和可靠性我喋喋不休,喋喋不休,唠唠叨叨的功能和时序验证技术(或缺乏)在1980年与我最初的ASIC设计。这是我大学毕业后的第一个位置。我是一个团队的成员设计的电脑主机cpu国际电脑有限公司(ICL)西戈顿曼彻斯特,英格兰。

1981年,两名经理的ICL形成自己的公司称为卷设计,随后,他们邀请我加入他们的行列。我们赚钱的方式在早期是写测试程序对印刷电路板(pcb)使用2225从GenRad测试人员。

绝大多数的董事会我们创建测试包括大量的“豆形软糖”逻辑集成电路(ICs)像SN54/74-series来自德州仪器(TI)。我们提供PCB,应该是“已知的好”(但通常不是)和一个原理图的修改应该匹配董事会通常(但没有)。

所以,第一步是采取摇(驴猜)作为目标函数的董事会,然后写一个测试程序,确保董事会工作。的一件事我很快发现的一些董事会发起者有任何测试的概念设计(DFT)。结果,我们常常必须创造性的关于内在逻辑状态到外面的世界。

2225年被列为functional tester(相对于针床测试)。董事会要测试通过其边缘连接器插入到2225,这意味着测试人员只董事会的主要输入和输出。

我们创建了我们的测试程序作为一系列的输入测试向量,每个定义为逻辑0和1的集合,以进入董事会。我们还定义了一系列预期的输出向量,每个指定为0和1的集合。

这些测试程序可能包含数千,有时数以万计的测试向量。由于董事会包含复杂的组合组合和时序逻辑功能,预期的输出是由不同数量的时钟周期延迟path-by-path基础上。

下一步是错误应用于电路板的一个节点,说做空逻辑门的输出。你然后运行测试程序,而实际的输出定义的预期输出你的董事会——是否检测到故障。如果没有,你必须重新审视你的测试程序来确定为什么它未能发现此错误,然后相应地修改程序。

你重复这个过程你可以适用于每一个可能的错误。哦,好玩。别急,还有更多,因为一旦你满意你的测试程序,你必须学习每个节点的“签名”。这里的想法是,你为2225提供了一种基于文本的网表的设计。测试人员有“飞行探测器”的结束。试验机指示你的地方调查第一销第一芯片,然后跑整个测试程序,捕获该节点上的0和1。再一次,你一次又一次地重复这个过程对于每个节点在黑板上。

所以,问题就在这里。董事会可能包含数千个节点,测试程序可以包含成千上万的向量,这可能是一个巨大无比的数量与每个节点相关信息,但记忆是非常昂贵的,在那些日子里非常有限。试验机的解决方案是使用一个16位的线性反馈移位寄存器(LFSR)来生成一个循环冗余校验(CRC)对于每个节点,从而缩小与节点关联的所有测试数据为16位CRC值(称为“签名”),被分配到节点。

现在,这正是事情变得很聪明。当董事会失败的领域,它被送往测试中心,连接成一个2225运行你的测试程序。操作员跑项目,确定哪些输出或输出提供不正确的签名。测试人员然后要求操作员将引导探针在芯片的输出驱动输出和重复失败的一个程序,以确保坏芯片的输出签名匹配坏板输出签名。

测试人员然后指示操作者把探头放在其中一个输入芯片,可能影响失败的产出和重复测试。如果这个输入签名是“好”,测试人员将继续下一个输入。如果输入签名是“坏”,测试人员会指导操作员把探头放在哪个芯片开车这个输入的输出。

最后,测试人员要么找到一个芯片坏输出和输入(即。芯片没有)或跟踪好的签名驱动芯片和一个糟糕的签名在接收芯片(即。跟踪失败了)。

我担心我简化事情有点,但我希望我已经设法传达过程的要点。我不得不说这是一个我生命中最奇妙的学习经验。除了提升我的逻辑技能,我被介绍给LFSRs, crc,甚至50字符编码称为基数的技术,允许您存储三个大写字母数字字符在一个16位的领域(见也技巧:压缩文本字符)。

卷设计有一个妹妹叫西锐公司电脑,商业化的小矿脉逻辑模拟器由1981年布鲁内尔大学的学生。虽然术语寄存器传输级(RTL)不在当时,帕克现在被认为是第一个真正的RTL模拟器。

新一代模拟器有三种口味:逻辑模拟器,min-max动态时间模拟器,和一个令人难以置信的复杂故障模拟器。我提到这个的原因是,我开始开发仿真模型,最终转移到卷云电脑,环游世界在逻辑仿真给予培训课程。这也是我第一次遇到了布莱恩•贝利,世卫组织目前正在编辑的技术在半导体电子设计自动化(EDA)工程。令人惊奇的Brian教我认为DFT和扫描测试和自动测试程序生成(生成),这是在起步阶段的超过35年前我笔这些话。

但这就是我想和你谈谈。

原因我在本专栏中闲聊,我只是聊天的男女真正的意图。最近,宣布他们的最新和最大的提供,这些小流氓说话Verix DFT,这是一个多模,全芯片的能力,DFT静态签字的工具。

测试是一个巨大的产业。测试插座时间是非常昂贵的,因此,任何可以被执行“左移位”和在开发周期中尽早解决问题,被认为是一件非常好的事情。这就解释了为什么Verix DFT最好部署在整个设计过程:

- 在RTL设计作为解决异步设置/重置的一部分,时钟,尽早和连接问题。

- 以下扫描合成检查扫描链服从规则。

- 后place-and-route(不)评估和正确的扫描链的问题重新排序或网表修改。

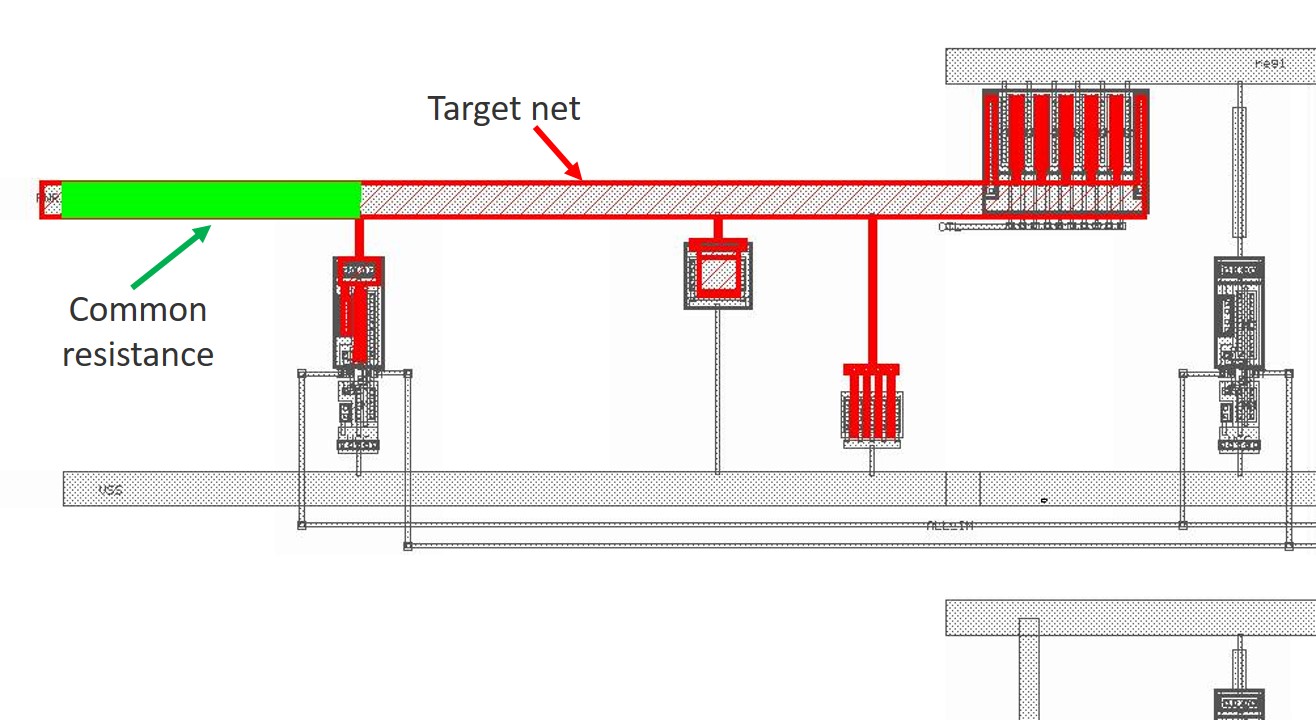

Verix DFT部署在整个设计过程(图片来源:真正的意图)

除了事实Verix DFT全芯片的能力,有三个关键方面的多模功能,减少安装时间和速度运行时,减少所花费的时间的调试和解决侵犯。在一个多模运行,该工具可以支持:

- 多个测试生成分区:Verix DFT可以节省大量的时间通过验证多个生成分区在每次运行,消除耗时的过程运行DFT静态签字为每个分区,每个分区要求自己的测试模式。

- 多个Constraint-Sets:Verix DFT使用设计约束验证DFT签署多个规则集约束的运行。每个约束集对应类型的生成模式,如未压缩,压缩,诊断,和连接。

- 多个Constraint-Sets多个测试模式:前两个功能的组合给了设计师的灵活性来验证多个constraint-sets多个测试模式。

在一个运行Verix DFT可以处理多个生成分区和多个DFT约束集(图片来源:真正的意图)

毫不奇怪,在真正的意图,而热情的人。老实说,很难让他们停止谈论Verix DFT的所有特性,功能,和能力。所以,为了让他们摆脱了痛苦,我将总结要点他们真的想让每个人都知道如下:

- 能力/性能:Verix DFT可以在几分钟内处理multimillion-gate设计完整的芯片容量和低峰值内存占用。

- 高覆盖率规则集:真正的意图使用一系列全面的规则来帮助确保高覆盖率的设计阶段,包括异步设置/重置,时钟,扫描链,触发器,端口和连接规则签收,和各种基本设置的检查。

- 细粒度的规则:细粒度的规则使更快地识别特定设计修复。

- 规则的选择和可配置性的测试模式:Verix DFT的规则可以有选择地启用在每个测试模式中,这样不同的测试模式可以各有不同的规则启用。事故的严重程度(错误、警告或信息)也是可配置的测试模式。

- 快速设置:Verix DFT很容易设置和使用,只需要几个小时,而不是几天或几周,可能需要与其他静态DFT工具。

- 聪明,分层违反报告:这个工具的准确、详细的设计分析提供了更精确的报告没有重复。Verix DFT的违反报告可以分层次分类违规,然后切换展开或折叠违反组。违反组织分级优先顺序,提供指导,帮助设计师更迅速地找到问题的根源问题。

- 集成iDebug:与真正的意图静态签字所有工具一样,人真正的意图已经集成iDebug调试平台提供图表便于DFT检查调试,cross-probing,轻松的豁免,可以运行之间移植。

- 根源分析和建议修复:rule-specific调试信息的图表工具标签,如故障源和复位故障规则融合实例。基于路径的完整调试路径显示违反规则的行为。此外,Verix DFT提供了精确的用户所需的指令设置更改来解决特定的违反。

- 故障覆盖率估计:Verix DFT估计有一个额外的工具选择故障覆盖率。当启用该选项时,将为每个测试模式,提供故障覆盖率和汇总评估整体扫描测试的故障覆盖率。通过自动估计的故障覆盖率为每个测试模式下,用户可以更好地优先考虑违反调试顺序和评估准备完毕。

唷!设计测试我不亲自做了,即使我想玩Verix DFT。对于那些是在测试行业,我想宣布Verix DFT的确是有趣的新闻。你呢?你把你的脚趾DFT水域?如果是这样的话,这将是伟大的如果你愿意在下面的评论中分享你的想法和经验。

你好,马克斯,

回到黑暗时代(1990/91时间)我有机会设计一个ASIC。当时现有的fpga不够足够大或快速处理我需要做什么所以我得蜻蜓点水式的asic。这是高密度脂蛋白信任之前这是一个充实的方案设计。作为流程的一部分,我不得不开发测试向量,可以用于软件设计和仿真,之后,用于实时信号注入打包死去。测试向量是专门格式的文本文件,所以我必须使用一个文本编辑器。的时候我做了100万多个向量生成(剪切和粘贴得到了真正的锻炼!)。芯片正常工作和工厂设施最终采用了设计作为他们的测试车辆。每当他们改变了过程或几何,他们会做一个运行我的芯片验证的新过程是好的,因为这些测试向量。他们这几年,直到被关闭了。这是当年几何测量在可怕的巨大微米。 I was working at 1.2, 1.0 and 0.9 microns, or 1200, 1000 and 900 nm for today’s crowd. Creating the vectors was a royal pain back then. Anything that can automate that process and still give good coverage is a total win. I solo designed two ASICs, and co-designed a 3rd before switching completely to FPGAs in the early 90’s. Never looked back.