SRAM到处都是这些天,主要在其嵌入形式。当记忆变得相对便宜或密度,它变得更加理想的包装健壮串成出类拔萃。

但是让我们面对现实吧:标准sram是一个痛苦的字节。他们大,要求6(甚至8)晶体管为每个内存存储。耗电,相对而言。为什么我们爱他们呢?当然,因为他们快。

6 t SRAM细胞标准费用很多,许多年,远比其他类型的电路。的第一个细胞被证明是一项新技术,它的亲切手绘,允许违反很多其他电路必须遵守的规则,并详尽测试证明它工作在各个角落——尽管违反规则的行为。然后铸造极其小心地守护它。

但一些裂缝出现在我们的基座放置6 t静态内存。我们看到的一个例子1 - t内存从芝诺在今年年初。从那时起,已经有更多的声音。所以今天我们看两个偏离常态,非常不同,但都试图解决一些限制我们不得不忍受为了绩效SRAM的速度在我们的系统。

打破了位线

我们从SRAM IP叫SureCore的公司。他们的目标是减少权力——尤其是动态功率。是的,他们想减少静态功耗,但泄漏的函数,这几乎是一个函数的底层技术——SureCore无法控制的东西。所以他们与动态功率降低。

他们有一些想法在低一些细胞,但他们一般关心的是晶圆厂不喜欢乱动,一些细胞,他们花了很多时间和精力。目前还不清楚他们是否会追求角度,但他们的主要推力已经离开细胞本身,而不是关注架构。特别是,他们发现位线是一个主要的参与者的能量消耗。所以他们做了一个改变,像任何改进,包括权衡,但是他们说提供了一个动态功率减少50%的记忆。

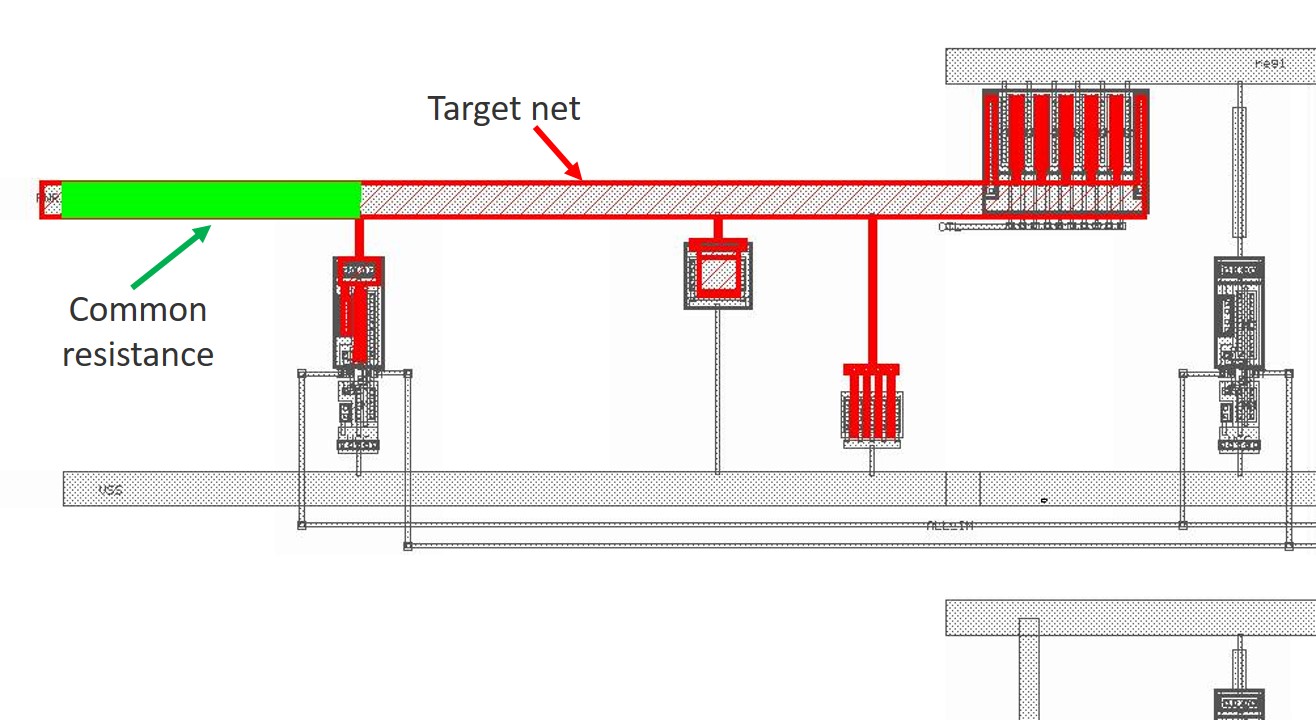

提醒一下,有点线的输出内存数组(而不是整个内存)。地址输入,或多或少,和大部分解决字线驱动器——也就是说,数组的行。然后列位线,虽然经常有比输出列的整体记忆,所以一些线mux到输出,和剩余的部分地址(比特不用于行地址)这些muxes驱动器。供参考,super-abstracted数组如下所示,与2:1 mux位线——也就是说,一个的地址确定哪些位线将阅读。(注意,“SA”代表“amp。”)

权力改变SureCore使得大幅下位线。问题是,就其本身而言,这种bit-line-lite不会强大到足以驱动后续电路(至少不与任何类型的性能)。所以他们已经添加了第二个阶段,作为高功率位线,除了他们,第二阶段分割成32位或64位-你的选择。每一个完整的位线,要快得多,它有权驱动信号。但因为这第二阶段不是拖着一长串的电容连接到细胞,它的速度和更低的权力。

事实上,在我进一步super-abstracted引渡这可能是什么样子(下图),这种安排的行为就像真实的位线被送入多路分配器由行地址。除了5(或6)行地址位的选择一条线使用作为输出。这可能看起来很奇怪有多路分配器由mux随后立即与解码以同样的方式;关键是增加驱动器。(更确切地说,这是我的抽象,不要以为他们的实际实现看起来就像这样——我无法得知他们的电路)。

这种力量的成本节省是一个在20 - 30%最高可能的速度和增加5 - 10%的内存的大小。它可以在40 ulp和28 FD-SOI流程。

对静态使用动态内存

下一个新的SRAM是一个令人惊讶的一个:取代静态细胞与动态。打赌你根本看不到它未来的发展趋势。这是导师图形coolSRAM-1T方法。

但这是交易:他们这样做不是一个过程,使用通常的DRAM过程模块,可以插入一个CMOS工艺,但只有标准CMOS工艺——不需要新模块。这意味着任何垂直晶体管或掩埋字线和网格(额外的机械支持)并发症。它也有像SRAM -这些RAS / CAS无稽之谈。

基本操作保留一些DRAM的特点。遥感是通过电荷共享:阅读时,位线是预先VDD的一半。然后选择细胞,和位线浮高或低,取决于电荷存储电容器的流入或流出。

当然,与DRAM一样,这是一个破坏性的读,所以读必须回写式紧随其后。回写式传感通过移动后会发生一些线全面恢复费用损失(或获得)在阅读。

然后有刷新,在大多数情况下,是需要看起来像标准DRAM刷新。

他们使用thick-oxide晶体管的选择晶体管。这种晶体管,通常用于I / o,必须与电压高于核心,操作调优提供类似的性能从节点到节点。用于细胞,它允许如果需要更高的电压。它也可以用于电容器,但是与激进的节点,他们改用金属帽。

他们不创建帽的两层金属(MOM),然而;相反,他们使用“边缘”电容:金属线之间的互电容的单层金属。维是由光刻控制以来,他们说这是更容易建立始终比metal-n-metal-n + 1帽。

看来有几个操作电压选项,考虑到大多数现代电路内部VDD和一个外部VI / O。数组和安培感觉可以运行在电压。使用一个高电压提供更好的性能和更强的信号,在更多的力量消散的成本。

内存也意味着更高的电压水平需要换档器,因为其余的芯片将运行在VDD。可能的组合是:

- 在V数组DD,感觉安培VDD。其余的芯片直接接口,使用VDD,所以不需要换档器水平。

- 在V数组I / O,感觉安培VDD。水平需要换档器阵列和安培。安培感直接驱动电路的其余部分。

- 在V数组I / O,感觉安培VI / O。这里还需要换档器的输出水平意义安培允许与低电压芯片。

因为多涉及计划——包括回写式和pre-charge读取,访问时间对于一个给定的银行是有限的。但它是可能的,推荐,甚至——构建总体内存架构,这样连续的读取顺序破裂将从相邻的银行——交叉阅读作为一个可靠的方法条纹数据到内存中。这允许更快的时钟,因为,当一个银行做帖子说清理,另一个银行可以忙提供输出。

这两种方法,SRAM世界被激起了。似乎有很多的关注,我们会留意去皮更多变化的主题。

更多信息:

你觉得SureCore和导师SRAM的创新?