我不知道你是怎么想的,但我已经开始觉得有点疲惫了。事情进展得太快了,我发现很难跟上。我仍然听到有人吹嘘“我们现在支持PCIe 4.0”,即使PCIe 5.0是自由漫游的,现在Rambus的人们正在向我介绍他们的PCIe 6.0产品。把我的嗅盐递给我,因为我还太小,不适合这种刺激!

为了确保我们都能跟上风笛的节奏,让我们提醒自己PCI Express (Peripheral Component Interconnect Express),缩写为PCIe或PCI-e,是一种高速串行计算机扩展总线标准,旨在取代旧的PCI、PCI- x和AGP总线标准。PCIe现在是计算机显卡、硬盘驱动器主机适配器、固态驱动器(ssd)、Wi-Fi和以太网硬件连接等的通用主板接口。

自诞生以来,PCIe的每个新版本的带宽都是上一代的两倍,所以没有什么大的惊喜。然而,如下图所示,发布之间的时间间隔反映了大约2017年的拐点。

PCIe的发展(来源:Rambus)

正如我们所看到的,PCIe 1.0于2003年推出,速度为每秒2.5千兆传输(GTps)。PCIe 2.0翻了一番,达到5GTps,而2010年问世的PCIe 3.0又翻了一番,达到8GTps。然后,我们不得不等待漫长的七年,直到16GTps的PCIe 4.0问世。这标志着我所说的拐点的开始,因为带有32GTps的PCIe 5.0在两年后的2019年出现,而PCIe 6.0在三年后的2022年出现,具有64GTps。

PCIe 6.0架构对于片上系统(SoC)设计人员来说是必不可少的,这些设计人员创建了需要在系统内移动大量数据的下一代设备,包括高性能计算(HPC)、云计算、人工智能/机器学习、企业存储、网络和汽车等应用程序。

此外,我的理解是,128GTps的PCIe 7.0预计将在2025年给我们一个愉快的“你好”,在我写这些话的时候,这只是短短三年的未来。

以防你不是精通的在这个主题中,“GT”(“千兆传输”)是标准的PCIe命名法。在单通道链路上,每秒64千兆传输相当于每秒64千兆比特。问题是,PCIe可以从1车道到32车道(实际上大多数人使用1、4、8或16车道),所以一个8车道的链路以64GTps运行相当于8 x 64 = 512Gbps。

我刚刚和马特·琼斯聊天,他是公司战略营销副总裁Rambus,它在PCIe IP的字段方面处于领先地位。Matt告诉我,PCIe 3.0和PCIe 4.0之间之所以有7年的差距,是因为没有一个杀手级应用程序,也没有一个进入第4代的驱动原因。但随后,我们开始看到数据生成、移动和存储方面的爆炸式增长——其中很大一部分是由人工智能(AI)和机器学习(ML)的日益使用所驱动的——这推动了第4代,随后是第5代,现在是第6代,很快就会是第7代。

今年早些时候,就在PCIe 6.0规范发布的时候,Rambus的伙计们发布了他们的PCIe 6.0控制器.只是为了刷新我们的记忆,PCIe 1.0到5.0使用非归零(NRZ)信令,每个时钟提供1位。此外,PCIe 1.0和2.0采用8b/10b(8位/10位)编码,而3.0到5.0采用128b/130b编码。相比之下,PCIe 6.0(以及即将到来的7.0)使用4级脉冲幅度调制(PAM4),这是一种多电平信号调制格式,每个时钟提供2位。

由于PAM4信令的误码率(BER)略高于NRZ信令,因此需要使用前向纠错(FEC)。反过来,FEC推动了将协议从可变大小的事务层数据包(tlp)转换为固定大小的数据包或流控制单元(flit)的需求,使用242B/256B编码。

我想知道使用FEC是否会降低系统的性能。Matt的回应如下:“前向纠错确实会让你付出一些代价,但还有其他机制在起作用,比如固定数据包大小会相应地提高效率。从效率的角度来看,使用任何数量的这些协议的问题都是小数据包和负载的开销。使用固定的数据包大小,其中一些是正确的,所以有效地你得到相同的吞吐量。”

Rambus PCIe 6.0控制器还支持L0p(发音为“ell-zero-pee”),它涉及动态车道分配以节省电力。例如,如果你的加速器和CPU之间有一个8车道的连接,它们通过PCIe相互通信,你可以通过执行“降档”来降低带宽并进入省电模式,如果你愿意的话,到一个4车道的连接。之后,您可以“升档”回到8车道连接。这方面的底层机制早就可用了,但它需要很多步骤才能实现。现在,随着L0p的引入,事情变得优雅多了。

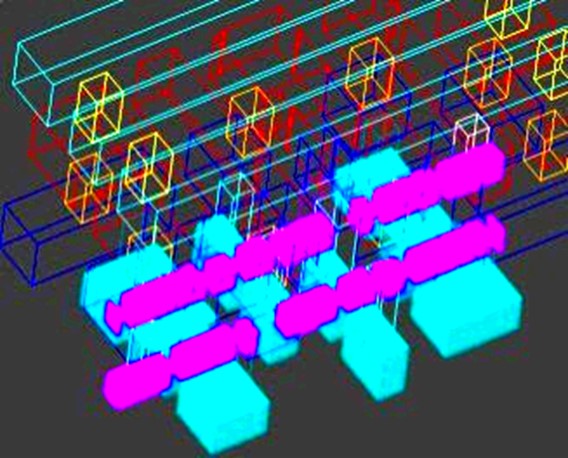

但我们离题了……马特和麦克斯的谈话,以及我在这里胡言乱语的原因是,Rambus的伙计们刚刚宣布了PCIe 6.0 SerDes PHY(物理接口),与他们的PCIe 6.0控制器配套。将这两种功能结合在一起的完整子系统为希望采用PCIe 6.0的客户提供了经过硅验证的性能。

Rambus PCIe 6.0接口子系统(来源:Rambus)

在SerDes/PHY中,物理媒体附件(PMA)子层执行序列化和反序列化功能,而物理编码子层(PCS)管理数据编码和解码功能。

我还应该指出,PHY块就是我们所说的“硬IP”,因为它是特定于进程节点的。相比之下,控制器是我们所说的“软IP”,因为它是作为RTL交付的,可以在任何进程节点中合成,因此与进程无关。

考虑这个问题的方法是,PCIe 6.0包括一个电接口(PHY)和一个协议接口(控制器)。这里提出的子系统概念涉及这两部分ip(它们都非常复杂和高性能),并为客户(工程师和系统开发人员)提供这个集成解决方案。这本质上是一个“现成的”PCIe 6.0解决方案,允许那些构建领先的asic和soc的人专注于他们自己的差异化内容,并为他们提供相对于竞争对手的上市时间(TTM)优势。

哦,是的,所有这些都支持最新最好的计算快速链接(CXL) 3.0标准,但恐怕我们不得不把这个话题留到以后讨论。与此同时,我一如既往地欢迎大家的评论和提问。

对不起,我有一个与本文无关的问题要问Max。例如,我饶有兴趣地阅读max的Switch debounce系列//m.morningcaffee.com/article/ultimate-guide-to-switch-debounce-part-4/

在什么程序中为这篇文章创建图表和时间课程?

谢谢你提供的信息

大家好——不用担心——我很高兴听到您正在阅读我的专栏文章(作为参考,第9部分包含所有早期专栏文章的链接//m.morningcaffee.com/article/ultimate-guide-to-switch-debounce-part-9/).Re the diagrams, I create them all in Microsoft Visio — I’m using the old Visio Standard 2010 version (so old it came on a CD I think you can get a web-based license of the current version for $5 a month. Also, there are free tools around for this sort of thing, but I really like the way Visio does things and I’ve spent so many hours using it that I really don’t want to learn anything else. I hope this helps.